本文以美信解串器96712为例,介绍已经应用于量产的视频数据通路功能。

1.基础介绍

在Serdes领域内,GSML一般指的是Maxim公司加串器与解串器之间的数据传输协议,目前已经有GMSL1, GMSL2和GMSL3三代。目前量产使用较为广泛的是GMSL2.本文介绍的解串器96712分别支持GMSL1和GMSL2。

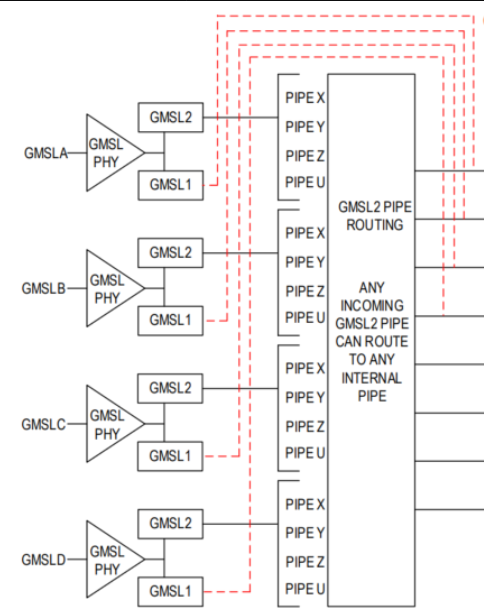

96712最多支持接入4v came数据,接口分别对应GMSLA ~ GMSLD(一般称为LINKA~LINKD)。每个LINK口,都具有四个Pipe selecttion,分别为PIPEX~PIPEZ。这里,LINK口用于物理连接相机模组,PIPE用于匹配与96712接入的加串器的PIPE,加解串器的PIPE需要匹配对应,否则,两者之间无法正确地建立Serdes数据链路。需要注意的是,有些加串器具有的PIPE是小于4个的·,例如,96717F只有PIPEZ,而9295E具有四个。那么,当96717F接入96712时,两者都只能使用PIPEZ了。

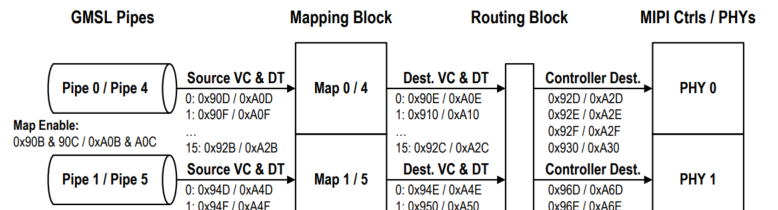

可以通过配置96712的0x06寄存器,来控制使用96712的GMSL1和GMSL2,配置寄存器0xF0~0xF4来控制96712的PIPE select。一般地,一路vc数据使用一个pipeline(一个pipeline可以传输多vc数据,此处不做讨论)。在GMSL1模式下,96712只支持4个pipeline,;在GMSL2模式下,96712支持8个pipeline。这里pipeline指的是经过前边GMSL Route后可以分配的数据通道,可以理解为line buffer。96712内有4个2lane的CSI DPHY,可以做拼接,拼成两个4lane的输出。

可以通过配置以下图示寄存器,建立从GMSL PIPE到96712 PHY输出的视频数据传输通路。

2.视频通路bypass

有了以上解串器视频通路配置的基本了解,这里介绍基于96712的视频bypass功能。

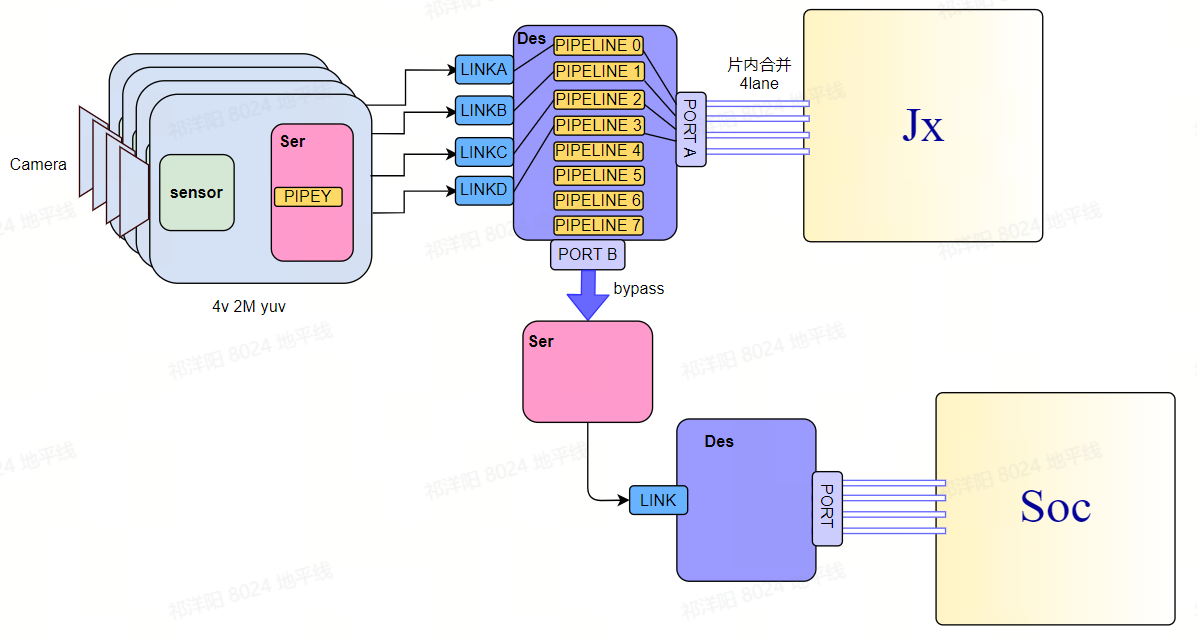

所谓bypass,指的是建立旁路数据通道,将前端camera数据送给两个SOC,如下图,4V图像数据,通过96712的port A输送给Jx(征程芯片),另外通过port B将同样的4V数据输送给另外的soc(在单soc行泊切换场景中,一般是IVI主机)。

对于96712,建立旁路数据通道有两种方式:

2.1phy copy方式

pipeline0~3的数据经过PHY0和PHY1从port A输出,通过phy copy方式,将PHY0和PHY1的数据 copy至PHY2和PHY3,从portB输出再经过一套Serdes传输至远端SOC;

phy copy可通过配置寄存器0x8A9, 0x8AA实现。

2.2route mapping方式

上文提到,96712 GSML2下有8个pipeline,可以直接将4v camera数据(4vc数据)mapping到8pipeline上,pipeline0~3和pipeline4~7是相同的4vc数据,前者从portA输出,后者从portB输出。

对于GSML1,没有pipeline4~7,要实现相同效果只能通过copy方式。

mapping方式可以通过以下配置实现,以下示例是将vc3的数据分别mapping到pipeline3和pipeline7,其它vc采用相同的方式。

3.视频通路解串器拼接----Superframe功能

不同的pipeline不仅可以传输相同vc的数据,还可以对多个pipeline不同vc的数据进行拼接,即96712的Superframe功能。该功能对图像同步精度要求较高,

同步精度差会直接导致soc收不到数据。

3.1竖拼

在解串器端将2vc数据拼接成单vc数据(Dual-view)送至SOC。

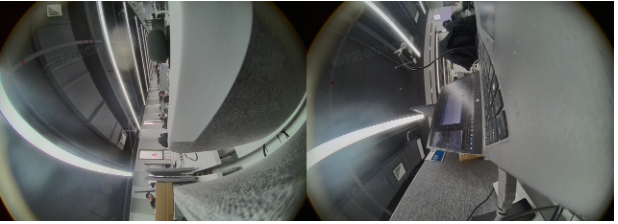

以下是将左侧2vc数据 2xWidthxHeight拼接成右侧1xWidthx2Height。右图是SOC收到的一张拼接后的图片。

3.2横拼

以下是将左侧2vc数据 2xWidthxHeight拼接成右侧1x2WidthxHeight。图示是SOC收到的一张拼接后的图片

通过调整以下寄存器,可以实现特定的拼接方式。