性能测试方法原理

CAMSYS其性能指标主要包括:帧率、延迟,以及系统的DDR带宽、CPU占用率等。

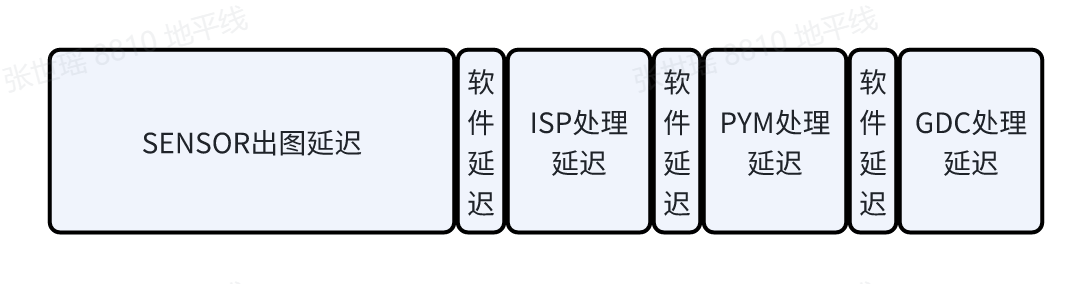

对于帧率、延迟,通过在驱动中创建trace event,分别记录通路上的每个IP,每帧开始处理(frame_start)和结束处理(frame_end)的时间戳信息和帧信息,来实现帧率计算和延迟统计。

帧率统计

每个模块处理完成后会产生一个frame_done中断,此时会记录下一个event点,此时在时间轴上每一帧则对应一个个离散的点。按照时间进行resample(重采样),得到每秒的帧率数据序列,此种方法可以较为直观的反应帧率变化。

延迟统计

对于延迟会统计两个数据,第一个是硬件处理引入的耗时,这个数据一般与处理尺寸相关相对固定,这个耗时称为模块延迟(module latency);另外一个是从cim 接受到一行数据产生frame_start开始到当前模块frame_end的耗时,这个耗时包括sensor的出图完成+前级IP硬件处理耗时+软件耗时,这个延迟称为到某模块的通路延迟(flow latency)。

模块延迟

只需要将该模块trace的帧event中的fe时间戳 - fs时间戳即可得到硬件处理耗时,即为module latency

模块 | 模块延迟含义 | 备注 |

CIM | CIM FE - CIM FS |

|

ISP | ISP FE - ISP FS |

|

YNR | YNR FE - YNR FS |

|

PYM | PYM FE - PYM FS |

|

GDC | GDC FE - GDC FS | 此处GDC FS 不代表中断,指得是配置寄存器triger硬件开始处理得时间 |

STITCH | STITCH FE - STITCH FS | 此处stitch FS 不代表中断,指得是配置寄存器triger硬件开始处理得时间 |

通路延迟

在trace的event中会传递cim的fs时间戳(timestamp),因此只需将模块的fe event时间戳-timestamp,即可得到从第一行像素输入开始到当前的整个通路延迟。

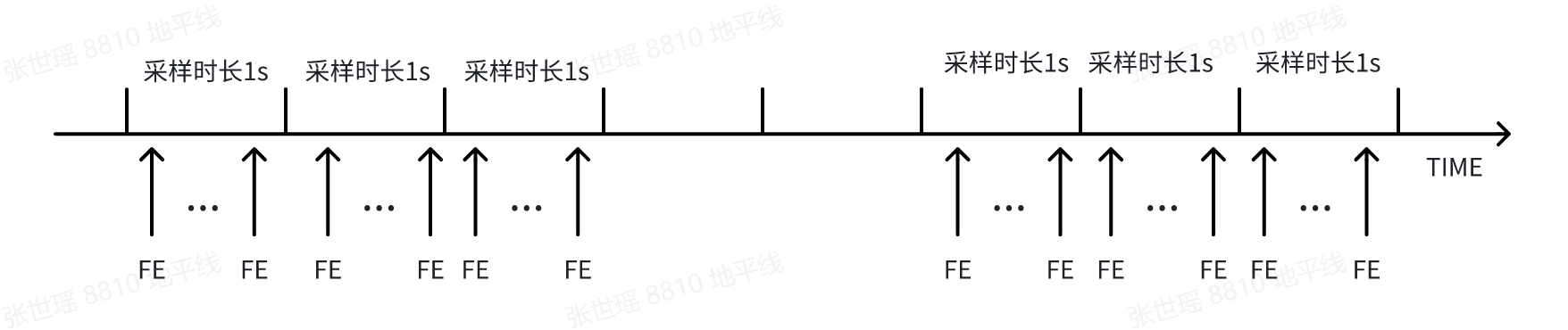

如以到GDC的通路延迟为例,那么统计的通路延迟就包含如图所示的所有延迟。

模块 | 通路延迟含义 | 备注 |

CIM | CIM FE - CIM FS | 等同于CIM的模块延迟 |

ISP | ISP FE - CIM FS |

|

YNR | YNR FE - CIM FS |

|

PYM | PYM FE - CIM FS |

|

GDC | GDC FE- CIM FS |

|

STITCH | STITCH FE - CIM FS |

|

CPU占用率统计

统计两个指标,一个是统计测试时CPU整体的load;第二个是开发工具统计感知通路相关进程以及内核线程造成的CPU开销。前者反应当前测试的环境的状态,后者反应CAMSYS 软件的开销。

DDR带宽统计

使用hurt_ddr工具获取DDR 读写信息,主要统计整体的DDR读写带宽与CMA SYS的读写带宽。

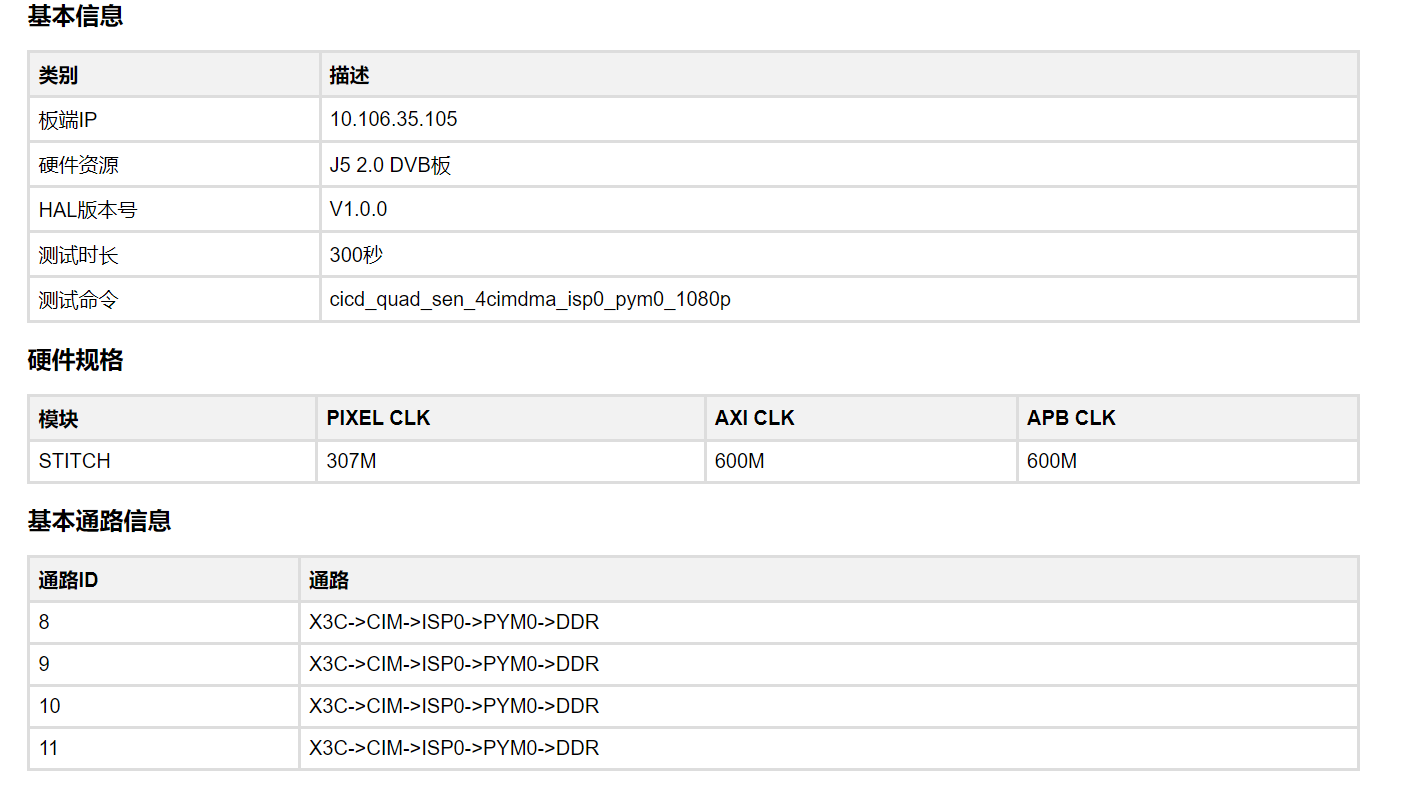

报告解读

基础数据信息中包含着测试环境、测试用例等固定信息

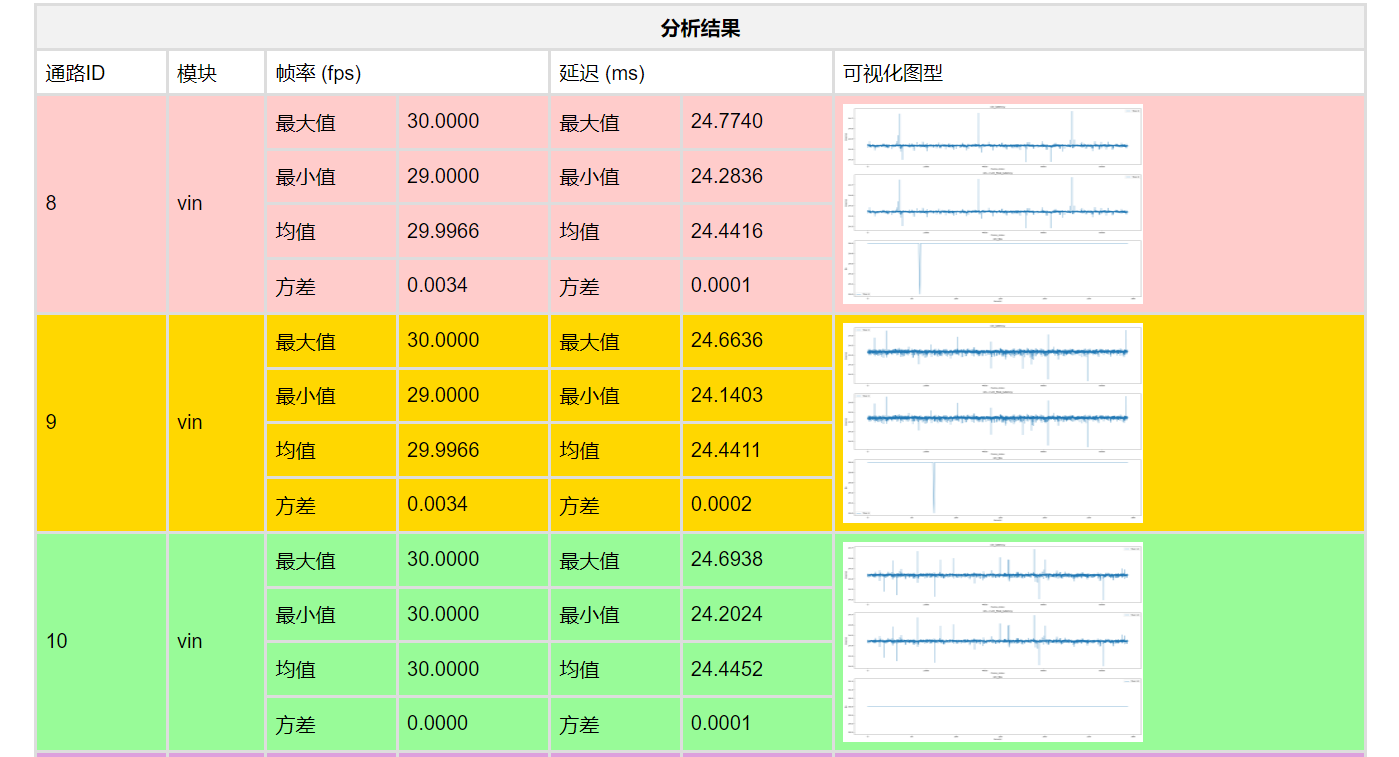

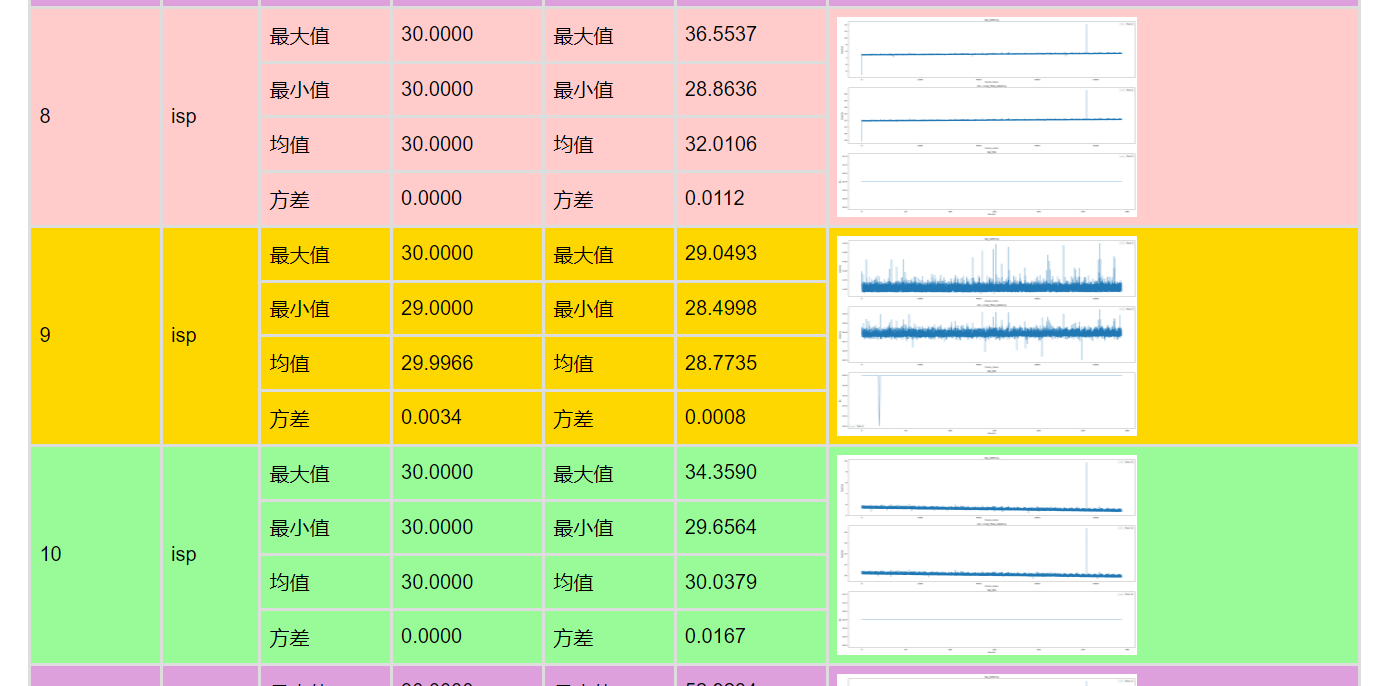

数据分析划分为两部分,第一部分为VPS的帧率、延迟分析,每个颜色块对应着某一条通路在该模块的帧率和延迟数据,其中延迟为到该模块的通路延迟。

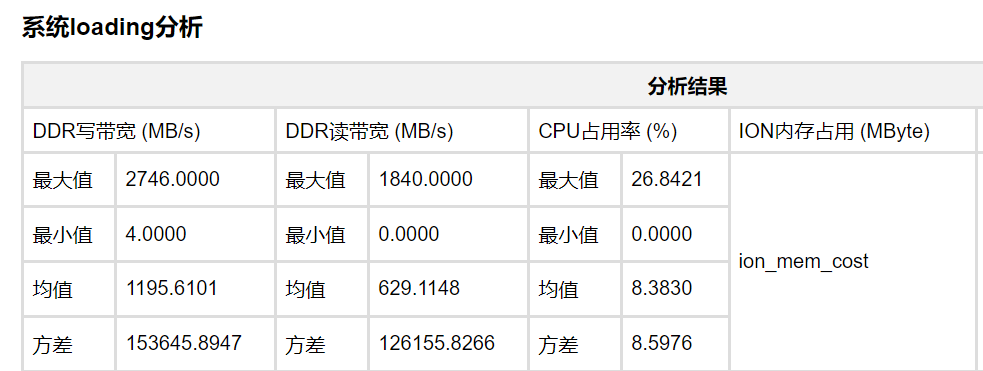

第二部分为系统load分析,包括系统整体的CPU、DDR load,也包括VPS对应的CPU load、CMA SYS 读写带宽

可视化图形解读

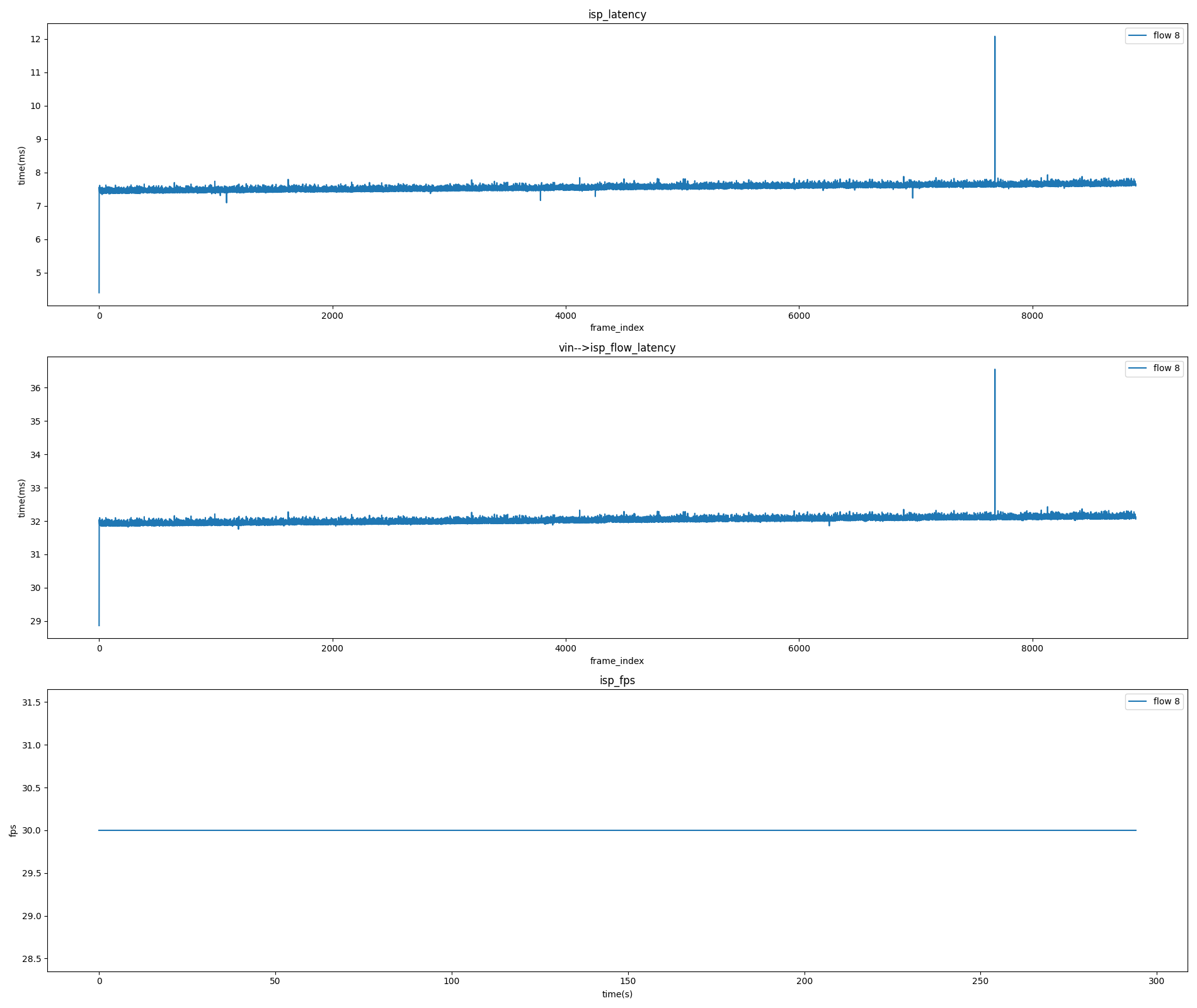

VPS的数据分析中, 每个模块的每个通路对应一个可视化结果: 第一个子图为模块的硬件处理耗时,纵轴为耗时(ms),横轴为帧序,如下图的isp_latency;

第二个子图为到该模块的通路延迟,纵轴为耗时(ms),横轴为帧序,如下图中的vin->isp_flow_latency;

第三个子图为对应的帧率统计序列,纵轴为帧率),横轴为时间(s)

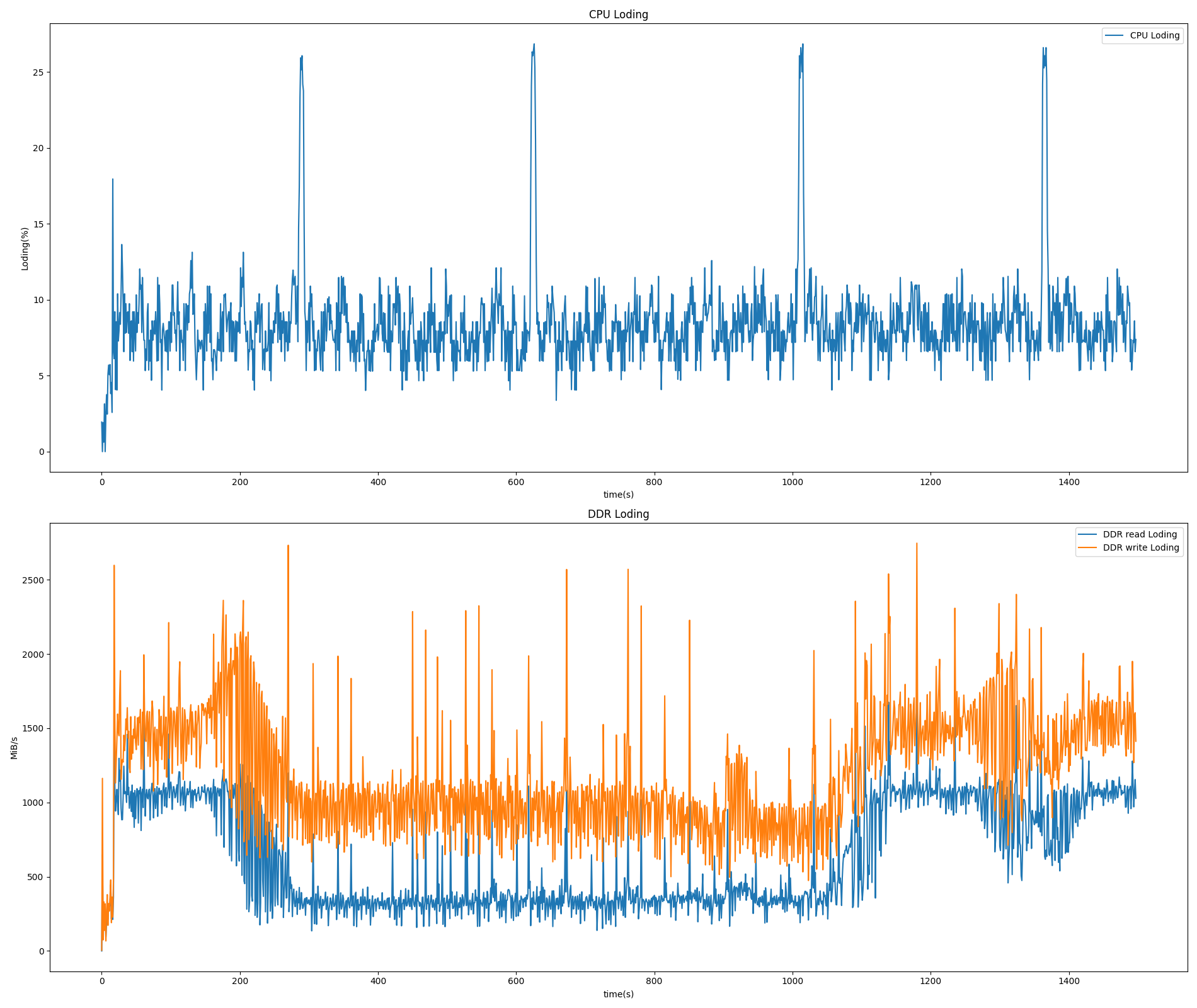

系统负载分析中,第一个子图为CPU load, 纵轴为loading(%),横轴为时间(s);第二个子图为DDR读写带宽,纵轴为带宽(MB/s),横轴为时间(s)。