算法通过了,系统挂了。这是自动驾驶测试里最扎心的一种失败。

一、22ms延迟案例:为什么SIL发现不了真实ECU的系统问题

深夜十一点,测试室的灯还亮着。

工程师盯着屏幕,闭环SIL(Software-in-the-Loop,软件在环仿真)已经跑了5000个场景,通过率100%。他从椅子上站起来,伸了个懒腰,心里有点飘——这套感知规划算法,在仿真世界里已经无懈可击了。

第二天,他把代码烧进真实ECU(Electronic Control Unit,电子控制单元),接上传感器,在HIL台架上重跑同一个场景。感知输出正确,规划决策正确,但执行器的响应晚了22ms。

没有报错,没有崩溃,日志干净得像什么都没发生。

但在量产评审上,22ms直接把整个项目打了回去。

评审官的话很简单:"高速场景下,22ms意味着30cm。你们知道30cm是什么概念吗?"

这不是在夸张。做个简单的物理计算:速度乘以时间等于距离。城市道路50 km/h时,22ms对应的位移是0.31米;高速行驶100 km/h时,是0.61米。感知输出"正确",但系统晚了半步——刹车、转向的指令晚了0.31到0.61米才送出去。

答案其实很简单,也很残酷——因为SIL是一个纯软件的世界。里面没有真实的ECU芯片,没有真实的驱动程序,没有CAN总线在跑时序。那22ms,藏在软件和硬件之间的缝隙里,而SIL这双眼睛,永远看不见那条缝。

二、SIL与HIL的区别:两道墙分别守什么

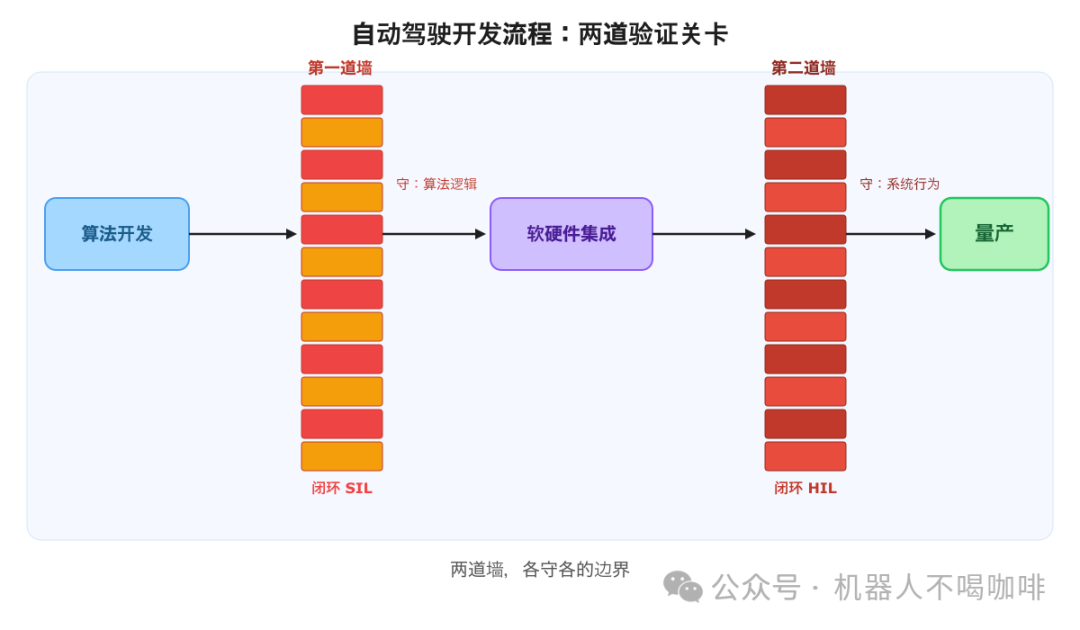

可以把自动驾驶的验证流程想象成两道关卡。

那条缝隙具体在哪里?可以把整个执行链想象成四段接力:

- 计算段:任务释放、抢占、中断响应

- IO段:驱动队列、DMA缓冲、数据搬运

- 总线段:报文打包、CAN仲裁、协议网关

- 执行器段:ECU到执行机构的指令路径

SIL通常会简化或跳过IO段和总线段,用理想化的stub代替。HIL明确把这四段全部接进来,让真实的时序和竞争重新出现——那22ms,就住在这四段接力的某个交接点上。

两道墙全景

两道墙不是谁替代谁,是开发流程里的串联关系:先过第一道,再过第二道。少了哪道,漏洞就会藏到更后面才被发现——代价越来越大。

行业有没有规定HIL必须测什么?

工程师的直觉是"测得越多越好",但测试资源有限,必须有人划边界。几个关键标准充当了这个角色:

三、传感器注入的四个层次:数据注入、MIPI注入、GMSL注入、物理光注入

在聊HIL怎么"骗"传感器之前,先看清楚一个真实摄像头信号的完整旅程:

Camera Sensor → MIPI(Mobile Industry Processor Interface)CSI-2 → Serializer → GMSL(Gigabit Multimedia Serial Link,千兆多媒体串行链路)同轴线 → Deserializer → MIPI CSI-2 → ISP(Image Signal Processor,图像信号处理器) → SoC

光线进镜头,变成电信号,被打包、序列化、传输、解包、处理,最终变成感知算法能用的图像。整条链路有七八个节点。

HIL的传感器注入,本质就是在这条链的某个节点"劫持"信号,塞进仿真世界生成的内容,让ECU相信它在和真实摄像头通信。切入点越靠近信号源(摄像头端),欺骗越彻底,工程难度也越高。

第一层:数据注入(ISP之后切入)

直接向感知算法喂处理好的图像数据,绕过了整条物理链路。Camera驱动栈、ISP处理流程、GMSL链路——全部旁路。这一层连"HIL"的门槛都勉强算不上,更像是SIL的变体。测的只是算法,不是系统。

第二层:信号注入(MIPI之前切入,Bayer RAW层)

在ISP入口处注入Bayer RAW信号——ISP(图像信号处理器)会完整走完 Demosaic、降噪、色彩校正等一整套处理流程。这一层"骗到"了ISP和驱动栈,但绕过了Serializer和GMSL链路。从MIPI接口往下的硬件都是真实的,往上的信号链是仿真生成的。大多数开发阶段的Camera HIL停留在这一层。

第三层:GMSL链路注入(Deserializer之前切入)

在同轴线接口注入符合GMSL协议的信号——整条从Deserializer到SoC的链路都是真实的,包括GMSL协议握手、Virtual Channel路由、I2C控制通道。

这里有个容易被忽视的细节:GMSL(Gigabit Multimedia Serial Link,千兆多媒体串行链路)在一根同轴线里同时承载视频、I2C控制通道和供电三路信号。HIL注入时,三路都要处理——光有视频信号不够,I2C通道不响应,SoC的摄像头驱动就会检测到异常,整条链路进入降级模式。

第四层:物理光注入(最深层)

用物理光源和光学系统照射真实Camera——从光子到Bayer RAW全部走真实物理路径。Sensor的量子效率曲线、CMOS的暗电流特性、镜头的光学畸变,全部原汁原味。代价极高,通常只在量产前的最终验证阶段才值得投入。

每往深走一层,工程复杂度指数级上升,但测出来的问题也越接近实车真实遇到的情况。这是一条没有终点的精确度阶梯——取决于你愿意在哪一层停下来。

四、Camera HIL注入为什么难:ISP、Black Level、Rolling Shutter与GMSL协议

MIPI层注入(第二层)听起来已经很"真"了——ISP从真实的物理接口拿到了信号,驱动栈正常工作,上层感知算法收到了处理后的图像。但ISP是个极其挑剔的"审计员",它的内部有一套完整的校正流程,每一步都对输入信号有隐性的物理预期。你的仿真信号只要在任何一步"露馅",后续误差就会一路放大。

进到第三层:GMSL协议的四道坎

第三层(GMSL注入)的挑战不只是信号内容,GMSL协议本身也要完整仿真。GMSL在一根同轴线里同时跑视频、I2C控制和供电三路信号,任何一路不对,SoC都会察觉。

五、LiDAR与Radar注入的核心难点:时序、Intensity与射频暗室

Camera注入的挑战主要集中在信号内容的物理真实性上,LiDAR和Radar面临的是另一套工程问题。

LiDAR

LiDAR不走GMSL,各家有自己的私有以太网协议——Ouster、Velodyne、Livox的帧格式互不相同,驱动栈也完全不通用。注入挑战不在于物理信号难以生成,而在于时序一致性:

旋转式LiDAR每一条扫描线都有独立的时间戳,精度要求在微秒级。注入帧的时间戳必须反映正确的旋转角度——差一点,驱动栈计算出来的旋转速率就会出现异常跳变,触发异常处理流程。

反射强度(Intensity)也是一个容易被忽视的维度。感知模型通常同时使用几何点云和Intensity信息做目标分类——道路标线的Intensity明显高于沥青路面,金属车身的Intensity和树木截然不同。纯几何点云注入缺少这层信息,感知模型的分类精度会系统性下降。

多传感器时间对齐是LiDAR注入里最核心的工程难题:LiDAR和Camera必须在同一时钟域里精确对齐。Camera帧有特定的曝光时刻,LiDAR点云有特定的扫描角度对应的时间戳,两者的时间差直接影响传感器融合的精度。

Radar

Radar感知的是电磁波回波,想骗它,必须在物理层造出真实的射频信号。任何纯软件层面的注入都是"绕过了物理"。高端HIL环境用射频暗室配合专业目标模拟器(Keysight或Rohde&Schwarz)生成真实射频回波——这套设备的成本在百万量级,只有量产前系统验证阶段才值得投入。

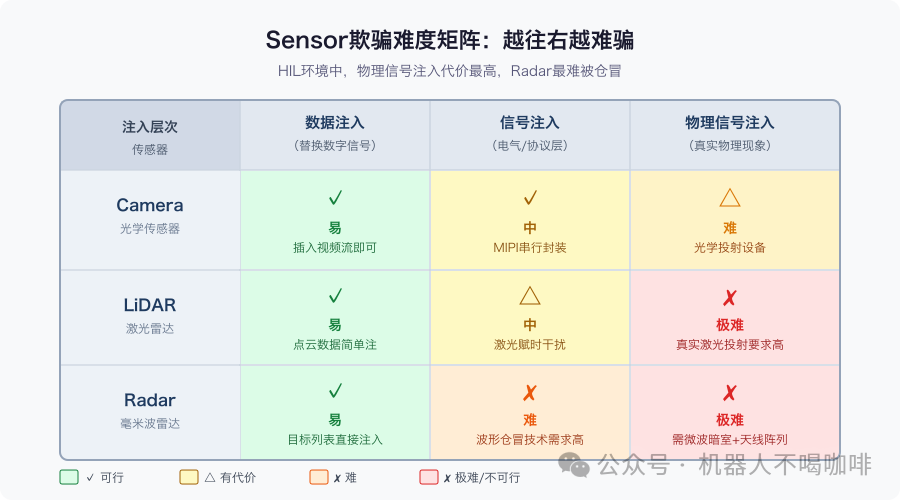

Sensor欺骗难度矩阵

从Camera到LiDAR再到Radar,被骗的难度依次上升——越靠近物理层,投入越高,测出来的问题也越接近实车真实遇到的情况。这条规律贯穿整个传感器注入工程。

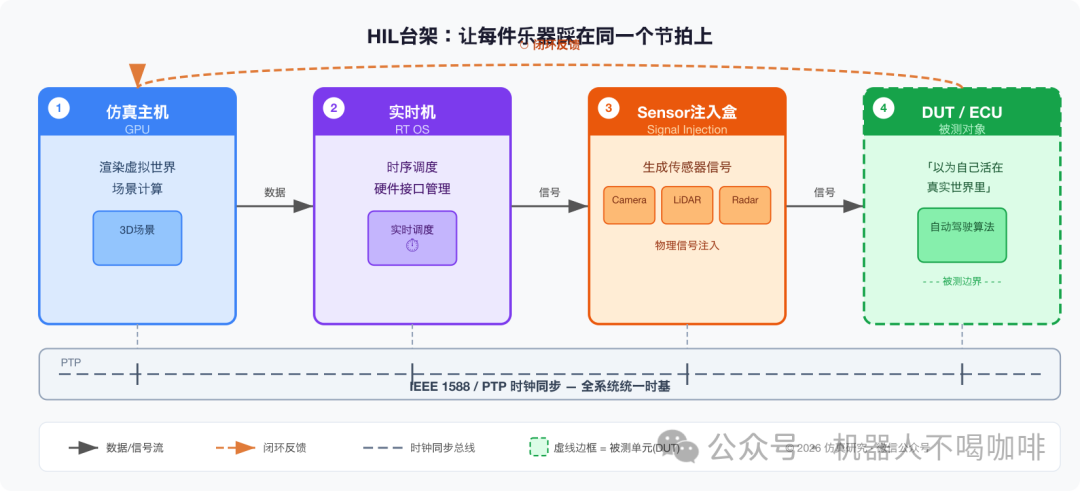

六、HIL平台硬件生态:dSPACE、Vector、NI、Speedgoat与Sensor注入硬件

想象一支乐队在录音室合奏。每件乐器必须踩在同一节拍上,任何一件抢拍或慢半拍,整首曲子的"真实感"就会在听众耳里崩掉。HIL系统就是这支乐队,搭建它需要一批专业化的"乐器"。

实时目标机(Real-Time Target)

实时目标机是HIL系统的"指挥",负责以1:1实时速率运行仿真模型并驱动所有接口卡。市场上有几家主流平台:

Sensor注入硬件

Camera:基于GMSL或FPD-Link协议的视频注入盒,本质是一块能生成符合协议的视频信号的FPGA板卡。dSPACE Video Unit是这个细分市场的主要产品之一。

LiDAR:按目标LiDAR型号定制的协议适配卡,通常是FPGA加以太网接口的组合,负责生成目标LiDAR的私有协议帧格式。

Radar:射频目标模拟器(Keysight、Rohde&Schwarz),价格极高,大多数开发阶段项目只做信号注入层。

软件层

dSPACE AURELION、NVIDIA DRIVE Sim等作为渲染后端,生成sensor仿真数据;ASAM OSI接口层负责仿真环境和注入硬件之间的数据格式对接,确保不同厂商的工具可以互联互通。

七、HIL平台采购还是自研:dSPACE一体化 vs 自研FPGA的选型逻辑

看完上一节的硬件生态,有人会问:直接买dSPACE的全套方案不就完了,为什么还要讨论"自己组装"?

现实是,这个选择没有标准答案,取决于你要测什么、要测多少台、以及你有多少时间。

一体化采购(购买整体方案)

从dSPACE SCALEXIO或Vector VT System买一套交钥匙方案,拿到手几周内就能跑起来测试。软硬件是同一家厂商设计的,接口天然兼容,技术支持有保障,工具链成熟。更重要的是,这些平台有ISO 26262工具鉴定文档(Tool Qualification)——量产认证过程中,你需要向审核方证明你的测试工具本身是可信的,买来的平台厂商会提供这些鉴定文件,自研方案需要自己做,成本不低。

缺点同样明显。一套完整的dSPACE SCALEXIO含sensor注入的配置,价格很容易超过百万人民币,而且是"一台一授权",如果需要50台测试台架,采购成本直接乘以50。另一个问题是定制化能力有限:如果你用的是一款新发布的私有协议LiDAR,或者一块自研的SoC域控制器,就不一定有对应的支持——要么等厂商跟进,要么付额外定制费,要么自己在平台基础上做二次开发。对于正在大量自研芯片和传感器的中国主机厂和Tier-1来说,这个约束越来越痛。

自研组装(Custom HIL)

自研方案本质上是:选一块高性能FPGA板做信号注入,选一套实时OS(QNX或Linux RT)搭实时目标机,选一个开放仿真框架(CARLA、LGSVL或自研引擎)做场景,再用开放标准(ASAM OSI、OpenSCENARIO)打通各模块之间的接口。

优势在大规模和定制化。当台架数量到了几十台,自研的单台成本可以做到一体化方案的1/3到1/5;面对私有传感器协议,自己写FPGA逻辑,不需要等供应商。国内已有头部主机厂(如蔚来、比亚迪、华为)在核心HIL能力上走自研路线,支撑自研芯片的闭环验证。

代价是前期投入巨大、维护负担长期存在。从零搭建一套能跑量产级别测试的HIL平台,通常需要6-18个月的工程投入,需要同时懂FPGA、实时OS、AUTOSAR、仿真引擎的复合型工程师——这类人才在市场上极度稀缺。更隐性的成本是工具鉴定:ISO 26262对测试工具有鉴定要求,自研工具需要自己写鉴定报告,这是一套严格的文档和测试过程,往往比想象中耗时。

实践中的混合策略

大多数成熟团队走的是"主干买、枝叶自研"的路:用dSPACE或Vector的平台作为实时目标机和总线接口的主干,保证稳定性和认证文档;在此基础上,针对私有传感器或特殊接口需求,增加自研的FPGA注入模块或定制化的接口卡。这样既保住了工具鉴定的基础,又有足够的灵活性应对定制需求。

八、AUTOSAR HIL为什么最难:时钟、总线、看门狗的连锁陷阱

硬件买回来,软件写好了,但让两者"相信对方是真实的",是另一回事。HIL的真正难点不在某一侧,在软硬件之间的协同。而量产ECU绝大多数跑的是AUTOSAR(Automotive Open System Architecture,汽车开放系统架构),这套架构把ECU软件切得极其精细,每一层都有自己的"挑剔之处"。

第一关:AUTOSAR的底层调用,一个都不能漏

AUTOSAR把ECU软件切成三层:SWC(应用层软件组件)→ RTE(运行时环境)→ BSW(基础软件)。HIL测试的被测对象是整个ECU的二进制镜像,含完整的BSW。这意味着仿真环境必须能正确响应BSW发出的所有底层调用——驱动、通信栈、诊断服务(UDS),一个都不能漏。

漏掉任何一个底层调用的响应,ECU就会进入异常状态——但日志里不一定有明确的错误信息。这类问题在联调初期最常见,也最耗时间:你看着界面一切正常,其实ECU已经在某个角落静静地不对劲了。

第二关:CAN Matrix对齐,差一位小数就是乱码

ECU通过CAN总线和外部世界通信,所有信号的名称、报文ID、字节顺序、物理量编码方式由DBC(Database CAN,CAN信号数据库文件)定义。HIL平台必须使用和ECU完全一致的DBC版本。

一个信号的字节序写反(Intel vs Motorola),或者缩放因子差了一位小数,ECU收到的就是乱码——但CAN总线的原始报文看起来完全正常。这类bug在总线层面找不到痕迹,问题藏在物理量解析逻辑里。经历过这种调试的工程师,大多都有被折磨几天才发现"是个小数点"的经历。

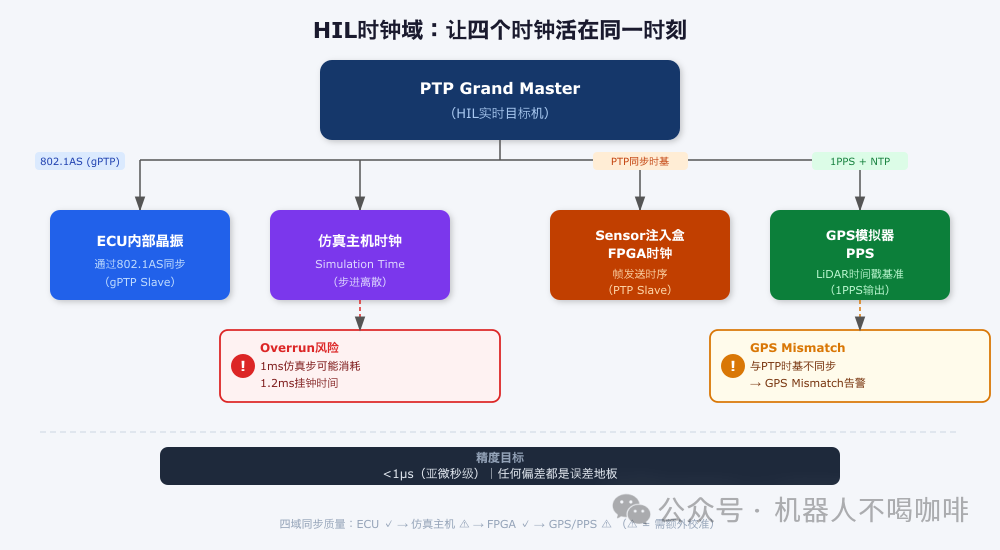

第三关:四个时钟,必须活在同一个时刻

这是整个AUTOSAR HIL里最容易出问题、也最难调试的环节。

一套完整的HIL系统涉及至少四个时钟域:ECU内部晶振时钟、仿真主机系统时钟、实时目标机硬件时钟、Sensor注入盒的FPGA时钟。想象四个人同时打节拍,每个人用的是不同的节拍器——乐队合奏出来的只会是噪音。

听起来简洁,但工程现实很残酷。

HIL时钟域架构

双时钟域:仿真时间 vs 挂钟时间

ECU的任务调度是严格的:快任务每1ms运行一次,感知融合任务5-10ms,规划任务20ms。Camera以30fps输出(每帧33.3ms),LiDAR以10-20Hz输出。这些周期都是基于真实硬件时钟打节拍的。

后果很隐蔽:ECU收到的传感器数据时间戳开始和自己的任务周期对不上。ECU以为这是10ms前的数据,实际上是12ms前的。没有报错,但传感器融合的预测步骤会产生系统性误差,最终体现为感知输出轻微抖动——你会以为是算法问题,其实是时钟漂移。

Jitter的软件层积累:无法消除的误差地板

真实车辆里,Camera的MIPI中断直达ISP,延迟在纳秒量级,Jitter极小。HIL台架上,同一条信号路径变成了:仿真引擎生成图像 → ASAM OSI接口层打包 → 传到实时目标机 → PCIe/以太网传注入硬件 → FPGA生成GMSL信号 → Deserializer → MIPI → ISP。每经过一个软件层,都会积累调度延迟和队列等待时间。

理论上PTP同步精度可以做到

WatchdogManager的定时炸弹

在HIL里,一旦仿真Overrun导致CAN总线报文比预期晚到,依赖这些报文的SWC可能无法在截止期内完成任务,Checkpoint超时,WdgM触发复位。复位日志里只写着"WdgM timeout"——没有"仿真超时了0.2ms"的信息。

九、4DGS能不能接进HIL:它能提升什么,不能解决什么

顺理成章地,有人会问:能不能把4DGS当渲染后端接进HIL,一步解决注入难题?

这个思路方向是对的,落地会撞上几道硬墙。

它是更好的"原材料",不是"解决方案"。真正藏着那22ms的地方,不在像素里。

十、HIL调试怎么找那22ms:CANoe、ControlDesk、Fault Injection与ASAM MDF4

当系统联调不符合预期,debugging往往是最消耗时间的环节。HIL调试有一套专用工具链。

总线监控

Vector的CANalyzer/CANoe是HIL调试的标配,可以实时抓取所有总线报文、做时序分析、比对信号值。当ECU行为异常时,第一步通常是在总线层面确认:信号有没有到达、时序是否正确、值是不是期望范围。总线是整个系统的"血管",大多数集成问题在这一层都有迹可循。

运行时监控

dSPACE的ControlDesk提供仿真侧的实时变量监控,可以同时观测仿真模型内部状态和ECU总线信号,找到"仿真侧发了什么"和"ECU收到什么"之间的gap。当两侧数据对不上时,gap出现的位置往往直接指向问题所在的接口层。

Fault Injection

ISO 26262要求验证失效模式的处理行为——某个传感器信号突然丢失、某条CAN线缆断开、某个ECU崩溃重启。HIL平台可以程序化地注入这些故障,观察系统的降级响应是否符合安全设计。这是HIL相比SIL最显著的优势之一:在台架上制造真实的硬件故障,观察整个系统的应对行为,而不是在代码里mock一个异常。

确定性问题

HIL调试里有一个棘手的特性:非确定性。实时系统的中断调度、CAN总线仲裁、OS任务切换都有微小的随机性,同一个场景跑两次,22ms可能变成21ms或23ms。这意味着偶发性问题很难稳定复现,需要长时间的统计测试和完善的数据记录。行业标准通常用ASAM MDF4格式记录所有总线信号和仿真变量,便于事后分析和问题定位。

找到那个"22ms",就是从海量的总线记录和仿真变量里,把延迟的来源一层层剥开——是驱动栈处理延迟、总线仲裁延迟、还是ECU任务调度的优先级配置问题。

经典失败模式一:Framerate Violation

Framerate Violation 是 HIL 里最高频的 Camera 相关异常,表现为摄像头驱动上报帧超时、帧丢失或帧计数跳变,但仿真看起来一切正常。

根因往往在时序链路的某个节点上:仿真引擎的渲染在这一帧多花了几毫秒(场景突然变复杂、动态物体增多),GPU 没能在规定时间内把渲染结果交给注入硬件。注入硬件的帧缓冲区空了,下一帧该发出去的时候没有内容可发。Deserializer 侧等待超时,向 SoC 驱动报告一次 frame miss。

帧计数器(Frame Counter)是另一个暴露点。Camera 每帧在 MIPI 元数据里带一个单调递增的计数器,驱动通过检测计数器是否连续来判断是否有帧丢失。仿真 Overrun 导致某帧被跳过时,ECU 侧看到的计数器从 100 直接跳到 102,驱动记录一次 frame drop,在 AUTOSAR 诊断日志里留下 DTC(Diagnostic Trouble Code,诊断故障码)。量产测试的 DTC 覆盖要求里,这个错误码是必须被触发并验证处理行为的——但在 HIL 里如果这个 DTC 被仿真超时偶发触发,就很难分清"这是测试覆盖到的失效模式"还是"HIL 台架本身的计算资源问题"。

多路摄像头的情况更复杂。前文(gmsl 章节)讲过 Deserializer 向所有 Serializer 广播 Frame Sync 信号来同步多路 Camera。在 HIL 里,如果四路摄像头的渲染完成时间不一致——Camera 0 在 T+32ms 完成,Camera 2 在 T+35ms 完成——注入硬件需要等所有路都就绪才能同步发出,等待期间 Frame Sync 信号会被拉长,SoC 驱动检测到多路帧的相位不一致,报告 frame sync error。这个错误和"某一路渲染超时"在日志里是两个不同的错误码,追因时容易绕弯子。

经典失败模式二:GPS/GNSS Mismatch

GPS Mismatch 指的是仿真引擎里车辆的位置,和 ECU 侧 GPS 接收机"看到"的位置对不上,导致传感器融合层出现定位跳变或异常告警。

实验室里没有卫星信号,GPS 接收机收不到真实的 L1/L2 频段射频。HIL 里通常有两种处理方式:一是用 GPS 信号模拟器(专用硬件,生成符合 GPS/GNSS 射频标准的模拟信号),二是直接向 ECU 的 GNSS 接收机注入 NMEA 报文或私有协议位置数据,绕过射频层。

更隐蔽的是时钟域问题。GPS 时间(基于 UTC,通过 PPS 信号同步)和 HIL 平台的 PTP 主时钟是两套独立的时间基准。LiDAR 传感器普遍使用 GPS PPS 信号来给激光脉冲打时间戳(Velodyne、Ouster 等主流型号均如此);Camera 的时间戳来自 SoC 内部 PTP 域。如果 GPS 模拟器的 PPS 信号没有和 HIL 平台的 PTP Grand Master 精确同步,LiDAR 的时间戳体系和 Camera 的时间戳体系会有一个系统性偏差,通常在几十微秒到几百微秒量级。

传感器融合算法(通常基于卡尔曼滤波或其变体)依赖各传感器数据的时间戳来做时序对齐和状态预测。几百微秒的时钟偏差在低速场景下影响有限,但在高速场景下,一个以 30m/s 行驶的车辆,200μs 的时间戳偏差对应 6mm 的位置误差——这个误差虽然绝对值小,但会让融合算法误判为传感器噪声增大,在连续积累后触发"定位置信度低"的告警,进而影响 L3 的控制权交接判断。

十一、L3自动驾驶测试为什么更离不开HIL:SOTIF、ISO 34501与控制权交接验证

L3自动驾驶系统把测试要求推到了新的高度。

L2测的是"辅助功能是否正确执行";L3测的是"系统能否在特定条件下安全地将控制权交还给驾驶员"。这个交接过程涉及跨多个ECU的状态机协同、严格的时序约束(从感知失效检测到发出接管请求的最大时延),以及驾驶员未响应时的降级策略。整条链路的任何一个环节出问题,最终呈现的可能是系统行为正常但时序不对,或者时序对了但降级路径走错了。

这不只是工程师自己的标准——监管机构也是这么要求的。联合国UNECE第157号法规(针对L3级自动车道保持系统)明确规定了系统在特定ODD内的行为约束和退出条件,要求能拿出可追溯的测试证据。Euro NCAP的辅助驾驶评级也在考察两件事:系统能不能正确辅助驾驶员,以及出问题时能不能安全降级——而这两件事的"出问题时",必须在真实硬件里制造出来才能验证。

说"SIL全绿",在这些评审和法规面前,是不够的。

下一篇我们会聊DCAS和Euro NCAP对自动驾驶仿真测试的具体要求——标准怎么定义"足够的测试",以及这些要求如何反过来影响HIL系统的设计。

十二、两道墙,各守各的

回到那个22ms。

如果那位工程师在SIL阶段之后、上车之前,还跑过一轮闭环HIL测试,那个延迟大概率会在台架上暴露出来——因为HIL跑的是真实ECU,测的是真实驱动栈和总线时序,藏不住。

开发流程是串联的:先过第一道墙,算法在仿真世界里验证通过;再接上真实硬件,过第二道墙,验证系统整体行为。少了哪道墙,那个"22ms"就可能一路藏到量产前才被发现——而那时候,代价要大得多。

不是谁替代谁,是各自守住该守的那条线。

这就是闭环HIL,第二道墙。

本文关键词速查

概念 | 一句话 |

|---|---|

闭环HIL | 让真实ECU和传感器相信自己活在真实世界里 |

欺骗四层次 | 数据注入→MIPI注入→GMSL注入→物理光注入,越深越难 |

ASAM OSI | 定义仿真组件接口规范,HIL互联互通的基础 |

ISO 26262 | 功能安全标准,决定HIL必须覆盖哪些失效模式 |

SOTIF (ISO 21448) | 功能没失效但行为不安全,L3测试的核心挑战 |

StbM + 802.1AS | AUTOSAR时钟同步模块+车载gPTP协议,精度 |

Framerate Violation | 仿真Overrun→帧缓冲空→DTC记录→多路Frame Sync错乱 |

GPS Mismatch | 先对时(PPS↔PTP),再对坐标精度,最后看位置值 |

一体化 vs 自研 | 台架少/ECU标准→买;台架多/自研芯片多→混合或自研 |

WdgM定时炸弹 | Overrun→CAN报文晚→SWC超期→ECU复位,日志只写timeout |

文章转载自公众号:机器人不喝咖啡

作者:九牧之